1.概述

1.1 适用范围

本测试方案主要针对SIP模块。如无特殊说明,DUT均指上述被测PCBA。

1.2 系统概述

测试软件采用JTAG.NET开发版开发,测试执行通过K1149a完成。

1.3 被测板描述

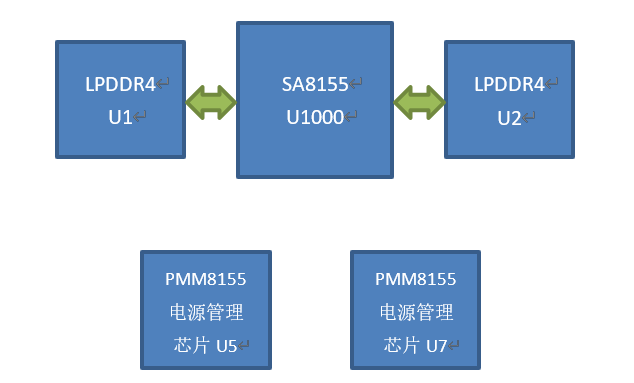

DUT由一片SA8155芯片及其外挂的2片LPDDR4组成,另外,DUT上还包含2片PMIC PMM8155用于提供各种电源。SA8155其他接口由位于DUT底部的BGA焊盘引出。DUT整体框图如下图所示:

2. 边界扫描测试扫描链设计

本方案采用BSI对DUT进行测试。SA8155的各功能引脚中,绝大部分有边界扫描单元,故通过BSI对其进行覆盖能够得到较高的测试覆盖率,测试效果良好。

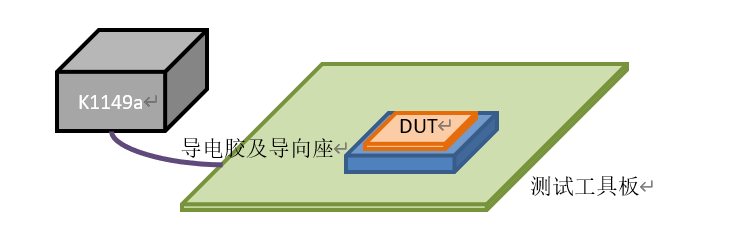

本方案测试系统的整体结构如下图所示:

测试系统由K1149a测试主机及测试工具板组成。

测试工具板通过导电胶与DUT进行连接,实现DUT的电源供电、测试信号连接及测试激励/响应的处理。

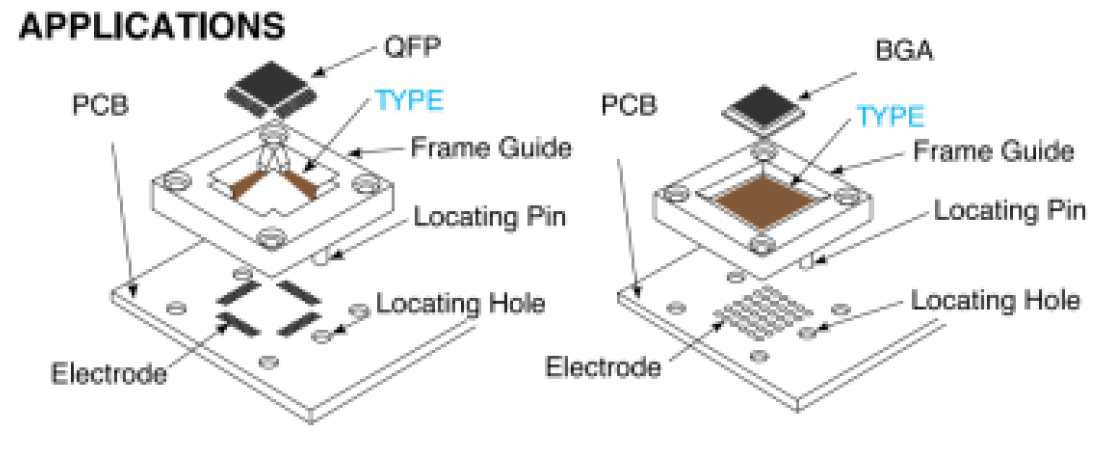

导电胶与工具板及DUT之间的接触方式如下图所示:

导电胶与固定在测试工具板上的导向座配合,实现DUT的定位,在DUT上施加一定的压力后,即可实现各BGA焊盘与测试工具板之间的可靠接触。

测试工具板根据DUT的供电需求,应提供DUT所需的所有电源种类,并按照DUT上电要求进行供电处理。

DUT的JTAG信号由测试工具板转接至K1149a测试仪表的TAP控制器,同时,测试工具板上对应的测试对接工具BS设备也由K1149a进行控制。

在测试工具板上与DUT对接的各信号,应按照DUT的电气要求完成对接,包括电平转换/阻抗匹配等。

DUT上PMIC的各路电源输出,在测试工具板上通过ADC芯片进行测试。

详细的测试工具板设计需基于DUT Datasheet并参考现有产品底板设计完成。

3 JTAG链路设计

本测试方案共设计2路TAP控制器,其中TAP1控制测试工具板上的BS设备;TAP2控制DUT。

4 测试覆盖分析

从SA8155的BSDL文件可以看出,芯片为绝大部分功能引脚均提供了边界扫描控制单元(共计442个),包括PCIe、GPIO、QLINK、CSI、DSI等。

未提供边界扫描控制单元的引脚包括USB2.0接口、WiFi接口及少量模拟/时钟信号

DUT的其他信号(主要是PMIC的各路电源输出),在测试工具板上通过ADC模块进行电压测量,实现测试覆盖。

经分析,DUT引脚覆盖率94.32%。

未覆盖的信号主要包括SA8155中不包含边界扫描单元的引脚即PMIC部分引脚。PMIC芯片由于不是边界扫描芯片,无法通过边界扫描进行直接控

制,其通讯控制接口SPMI无测试dummy,部分信号无法覆盖。

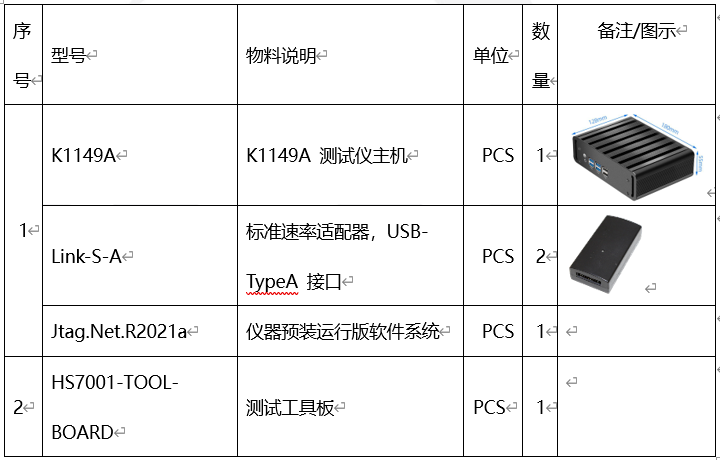

5 物料BOM清单

公司地址: 广东省深圳市福田区梅林路46号天欣大厦301B

联系电话: 13316846676

电子邮箱: sales@zhjtag.com