初识Jtag--Boundary Scan(三)

Part4:TAP控制器

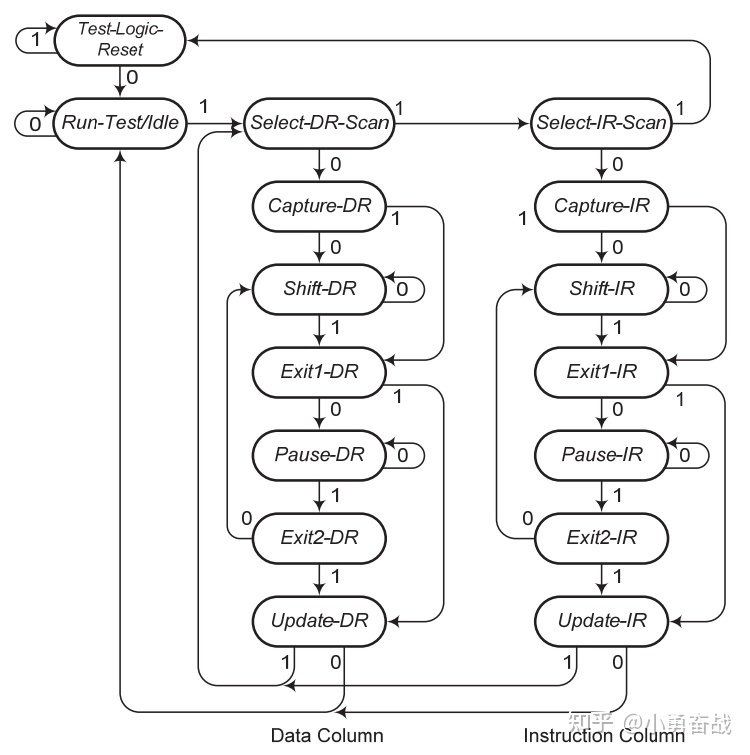

图8:IEEE 标准下的TAP控制器结构示意图[3]

对,TAP 其实是一个拥有16个状态的状态机。该状态机由 TCLK 和 TMS 信号驱动( TMS信号闪亮登场 ),完成状态的跳转。从整体结构上看,整个状态机分为两大块,图8右侧的指令Scan 和左侧的 Data Scan。Test-Logic-Reset 为初始状态和复位状态。在此状态机的任意一个状态,保持 TMS 信号至少 5 个周期的高电平,状态机会进入复位状态(不信你可以自己试试)。

1、Test-Logic-Reset

状态机的初始状态。在此状态下,IEEE标准指导的是默认加载一个叫做 IDCODE 的指令。小插曲:哎,这个指令刚好对应这个前面所说的设备识别寄存器 。如果当前的 Jtag 没有配置设备识别寄存器,默认加载的是 Bypass 指令。

2、Select-DR-Scan 和 Select-IR-Scan 以及 Run-test/Idle

临时状态,不做具体的操作,详细的各位可以去查IEEE 1149.1标准(文后我会给出链接)。

3、Capture-IR

还能回想起来之前在描述指令寄存器的时候,说过它的工作模式的问题吗?当 TAP 控制器处于 Capture-IR 状态时,指令寄存器执行捕获的操作,也就是将 Din 上的数据并行加载到指令寄存器中来。

4、Capture-DR

虽然数据寄存器有很多,但是就前面所聊到的那些寄存器是不是也都有 Din 端口。当 TAP 控制器处于这个状态时,对应的数据寄存器则将 Din 上对的数据并行加载到寄存器中来。啥叫“对应的寄存器”? 这个我们在 Part 5中进行解释。

5、Shift-IR 和 Shift-DR

指令寄存器或数据寄存器执行移位的操作

6、Exit1-IR、Exit2-IR、Pause-IR

在执行 JTAG 操作时,有的时候测试向量缓存很小,缓存空了但是激励还没给完,需要等待一下,那么这三个状态就发挥作用了。就是一个等待的过程然后进行状态挑战

7、Exit1-DR、Exit2-DR、Pause-DR

同上。只不过这个是防止接收缓存小而导致接收缓存满了的问题(个人理解)。

Updata-IR: 指令寄存器完成移位后,对数据进行“锁存更新”,便于输出。(可以看看图3)

Update-DR: 数据寄存器完成移位后,对数据进行“锁存更新”,便于输出。(可以看看图7)

接下来我们较为完整的阐述一下整个状态机的处理流程。系统上电后,TAP控制器进入Test-logic-Reset 状态。然后依次进入 Run-Test/Idle → SelectDR-Scan→ Select-IR-Scan → Capture-IR → Shift-IR → Exit1-IR → Updata-IR, 最后回到 Run-Test/Idle。在 Capture-IR 下,一个特定的逻辑序列被加载到指令寄存器中;然后 TAP 进入 Shift-IR 状态。在该状态下,受 TCLK 时钟控制,一条特定的指令送入移位寄存器并进行移位的操作。在Updata-IR 状态下,移位寄存器中的数据(指令)送入更新指令寄存器中。最后回到Run-Test/Idle ,完成指令的加载。

一般而言,指令加载完成后,进行数据Scan的操作。以为起点,依次进入SelectDR-Scan → Capture-DR → Shift-DR → Exit1-DR → Updata-DR。最后回到 Run-Test/Idle。在此过程中,数据寄存器会被配置到 TDI-TDO 之间(可以理解为点到点之间的串行连接)。在Capture-DR 状态下,TCLK 的驱动, 芯片管脚上的输出信号会被“捕获”到相应的边界扫描寄存器单元中去。这样,当前的数据寄存器当中就记录了芯片相应管脚上的输出信号。接下来从 Capture-DR 进入到 Shift-DR 状态中去。 在 Shift-DR 状态中, 由 TCK 驱动, 在每一个时钟周期内, 一位新的数据可以通过 TDI 串行输入到数据寄存器当中去,同时,数据寄存器可以通过TDO 串行输出一位先前捕获的数据。在经过与数据寄存器长度相同的时钟周期后,就可以完成新信号的输入和捕获数据的输出。 接下来通过 Exit1-DR 状态进入到 Update-DR 状态。在 Update-DR 状态中,数据寄存器中的新数据被加载到与数据寄存器的每个寄存器单元相连的芯片管脚上去。最后,回到 Run-Test/Idle 状态,完成对数据寄存器的访问。

Part5:指令寄存器和数据寄存器

回到图2,图2中是不是还有一个解码单元。这个解码单元是指令寄存器和数据寄存器的桥梁。当TAP完成指令加载后,也就是现在Jtag知道自己要做什么事了。指令寄存器中存放的指令经过解码单元进行译码,从而选中与指令对应的数据寄存器。比如 Bypass 指令则选中旁路寄存器;IDCODE指令选中设备识别寄存器。

Part6:指令和数据的加载过程示例

(1)指令的加载

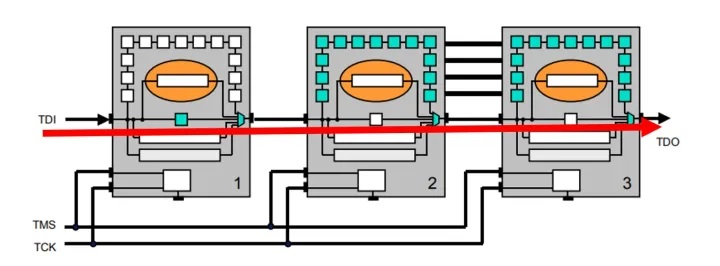

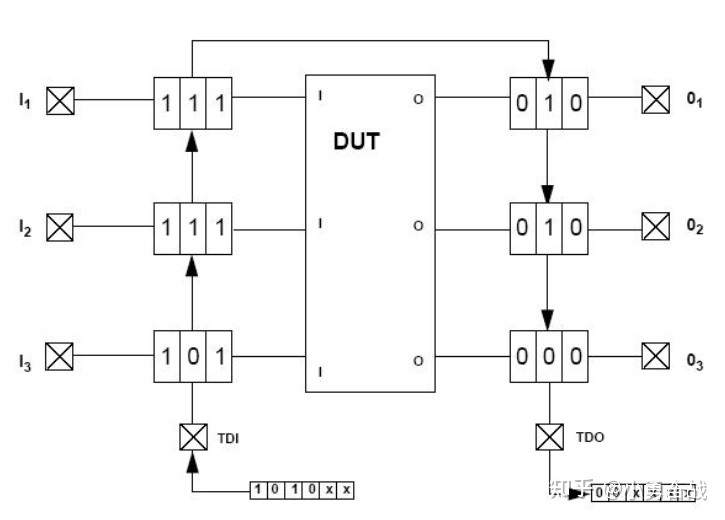

我们现在假设每个Chip上的指令寄存器都是2bit。旁路指令编码为11,采样指令编码为00(我们暂时可以不管这个指令到底是干嘛的)。现在需要将指令送入这三个chip,并让chip1指令旁路操作,而chip2和chip3执行采样操作。当TAP控制器在 Shift-IR 状态下时,将指令寄存器配置到TDI-TDO之间(如图9所示的串行连接结构,红色箭头所示)。从左侧TDI上串行灌入指令序列110000,经过6个cycle的移位后,当前chip1的指令寄存器(或者移位寄存器)中为11,chip2和chip3为00。这个时候我们认为移位完成,控制 TMS 让状态机进入Updata-IR。这个时候每个chip的指令移位寄存器中的数据送入指令更新寄存器完成指令加载的操作(时刻牢记指令寄存器和数据寄存器的工作模式)。

图9:指令的加载配置示意图[1]

(2)数据加载

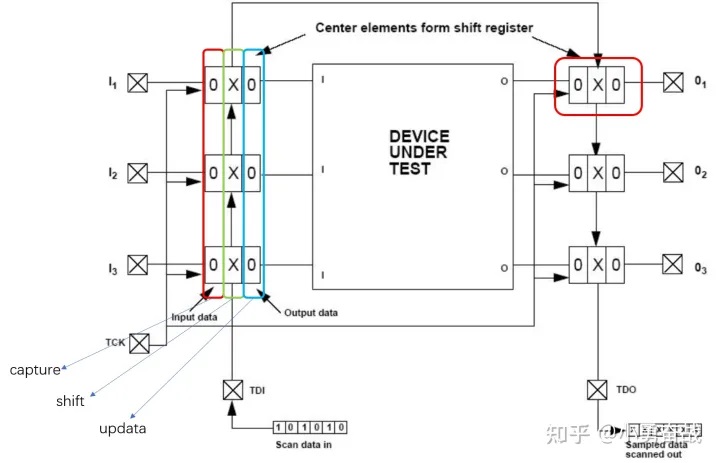

终于找到更为直观的图了,解放了!请看图10。图示更为形象的将数据寄存器的工作模式体现了出来。红色的可以理解为给Cupture-DR服务的寄存器,绿色的时给Shift-DR服务的寄存器,蓝色的是给Updata-DR服务的寄存器。

图10:数据寄存器的操作过程[4]

图10中给出的示意图是准备进行数据Scan的操作,此时假设整个扫描链中的寄存器都是未知态X。移位寄存器和TDI-TDO串行连接。现在需要将101010这个序列送入整个边界扫面单元。

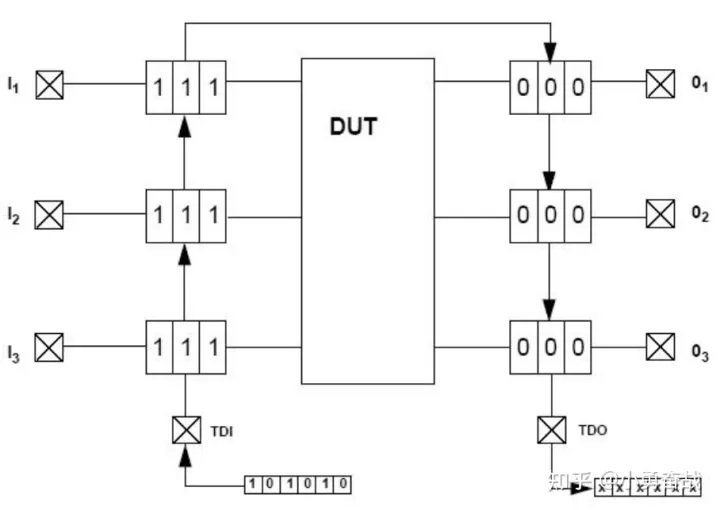

TAP状态机首先进入Capture_DR,在一个 TCLK时钟的驱动下, 芯片管脚上的信号状态全部被捕获到相应的边界扫描移位寄存器单元当中去(如图11)。接着进入Shift-DR,这个时候进行串行移位的操作。图2给出了经过两个时钟移位后的示意图(每个时钟一个bit)。经过6个时钟移位后,TAP控制器进入Updata-DR状态,完成状态的更新。而原先在由 Capture-DR捕获到的并送入 Shift-DR, 则通过 TDO 输出到了外部。

图11:Capture_DR[4]

图12:Shift after 2 cycles[4]

图13:Updata-DR[4]

公司地址: 广东省深圳市福田区梅林路46号天欣大厦301B

联系电话: 13316846676

电子邮箱: sales@zhjtag.com